直接交换数据的内部存储器。它可以每时每刻读写(刷新时除外)且速度很快,通常作为或其他正在运行中的程序的临时数据存储介质。ram工作时可以每时每刻从任何一个指定的地址写入(存入)或读出(取出)

ram在计算机和数字系统中用来暂时存储程序、数据和中间结果。随机存取存储器(ram)既可向指定单元存入信息又可从指定单元读出信息。任何ram中存储的信息在断电后均会丢失,所以ram是易失性存储器。本文主要介绍ram的结构和读写过程。

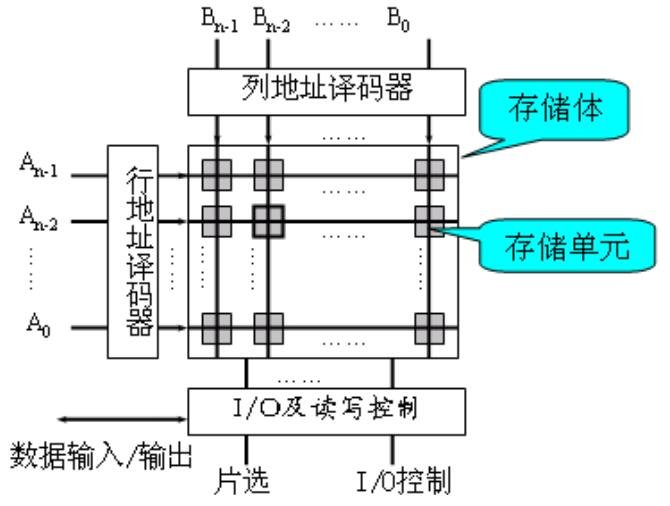

1)行、列地址译码器:它是一个二进制译码器,将地址码翻译成行列对应的具体地址,然后去选通该地址的存储单元,对该单元中的信息进行读出操作或进行写入新的信息操作。

2)存储体:它是存放大量二进制信息的“仓库”,该仓库由成千上万个存储单元组成。而每个存储单元存放着一个二进制字信息,二进制字可能是一位的,也可能多位。

例如一个10位地址的ram,共有210个存储单元,若每个存储单元存放一位二进制信息,则该ram的容量就是210(字)×1(位)=1024字位,通常称1K字位(容量)。

3) I/0及读/写控制电路:该部分电路决定着存储器是进行读出信息操作还是写入新信息操作。输入/输出缓冲器起数据的锁存作用,一般会用三态输出的电路结构。因此ram可以与其它的外面电路相连接,实现信息的双向传输(即可输入,也可输出),使信息的交换和传递十分方便。

访问某地址单元的地址码有效,假如你想去访问的具体地址:如A9~AO=OD3H=0011010011B,

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章FPGA片内

是FPGA中常用的基础模块,可大范围的使用在缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家

RMA是内存得简称,叫做Random-Access Memory(随机存取存储器) 是计算机得重要组成部分 1、Random-Access Memory(随机存取存储器):在计算机的组成

在计算机和数字系统中用来暂时存储程序、数据和中间结果。随机存取存储器(

在计算机和数字系统中用来暂时存储程序、数据和中间结果。随机存取存储器(

上千差万别,如何根据具体的测量目的、测量对象以及测量环境合理地选用传感器,是在进行某个量的测量时首先要解决的问题。当传感器确定之后,与之相配套的测量方法和测量设备也就

技巧,将从查看文档开始,到最终完成完整的程序。单片机型号:STM32F070F6P6步骤如下:1、查看文档

丘里管节流量水装置是有节流喉道,差压计和导压管三部分构成。标准(经典)

耗费大量的动态存储器,所以大部分程序会取折中的方法,将需要快速运行的部分和要

个很重要的部分就是存储器。存储器是用来存储程序和数据的部件,对于计算机来说有了存储器才有记忆功能,才可能正真的保证正常工作。存储器的种类很多,按其

位为12*512=6144 ,故实际使用率为6144/8192=75%,当所有fifo都按照这种配置来分配时FPGA中的

致的。可是读的时候,local_rdata数据正常,可是dq却出现错误。请问这是什么原因呢?还有个

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言

通讯的起始和停止信号数据有效性地址及数据方向响应STM32的I2C特性及架构通讯引脚时钟控制逻辑数据控制逻辑整体控制逻辑

OpenHarmony(以下简称“OpenHarmony”) liteos_m内核采用了littlefs作为默认的文件系统。本文着重

次使用FreeRTOS构建STM32的项目,踩了好些坑,又发现了我缺乏对于操作系统的内存及其空间的分配的知识,故写下文档记录学习成果

下前面3个参数:1.Address setup time: 从设置引脚地址开始到能够读取数据的时间段2.Data setup time: 设置完地址后,能够读取数据总线烧

般不超过512kbyte,Flash最多2Mb,咱们这篇文章,主要是关注内存(即

体,如下: #pragma pack(push) //保存对齐状态 #pragma

Verilog HDL 中的主要行为通过两种语句来控制进行:• initial 语句

智能屏 单独强大的51系统框架 资源充足,频率高。我对原来工业控制加热设备部分简化

下程序移植,基本达到目的。 实现工业控制加热设备等功能。硬件框架如上图所示,硬件部分基于 迪

480*480分辨率的4寸智能触摸屏,4寸的方屏刚好可以放在86型开关面板上,也就是我们家用的开关面板。所以显而易见这款迪

本帖最后由 TLLED 于 2022-2-11 11:38 编辑 今天来搭建迪

屏DMG85480F050_01WTC主控1:esp32主控2:air105LCD:显示camera图像,用于扫码

由M9K存储器模块组成,通过这一些M9K存储器模块进行配置,能轻松实现各种存储器功能,

的完成。在CaldRvI2I2CyRead()之后,怎么样才可以看到进程何时完成?我尝试调用

各位高手,小弟正在使用MICODER集成开发环境向庆科的micokit 3165开发板烧写程序,烧

本帖最后由 runileking 于 2016-4-14 17:56 编辑

定的操作。接着是写等待数据状态,此时根据片选信号CS0和CSl的值译出SEML、CEOL、CElL,并输出有效的地址和控制信号R WL、UBL、LBL到双口

的SDRAM接口设计,为需要大容量存储器的电路设计提供了新思路。关键词:SDRAM 解复用 接口 存储器

是FPGA中常用的基础模块,可大范围的使用在缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC

主机由从机中读数据:通讯复合格式:2.通讯的起始和停止信号3.数据有效性4.地址及数据方向5.

进行初步的分析。以读出操作为例,首先是读信号和地址信号有效,然后在内部时序电路的控制下,对存储阵列中的位线进行预充电,接下来行、列译码器输出,选中相应的存储单元的字线怎么

程序吗?最好是基于DSP2812或者DSP28335的例程。自己调试了许久,未能成功。

了通过并行接口扩展单片机片外内存的方法。在STC8H8K单片机运行在40MHz总线的情况下,完成片外

仅仅需要0.5微妙。这在很多情况下能够完全满足单片机数据访问的要求了。但是通过单片机的...

自主研发的超高的性价比双核T5L系列芯片,将整个智能屏核心电路放到PCB板子上,集成整合触摸屏(电阻触摸和电容触摸

存储器中数据在掉电时的三种保护方法及相应的设计电路和软件设计方法,以便更可靠地保护

的并口设计应用 摘要:IDT7132/IDT7142是一种高速2k×8双端口静态

pygit是一个大约500行Python代码工具,实现了一些git功能,包括创建库、将文件添加到索引、提交、将自身推送到GitHub上去。 本文给出了一些代码编

2bits,原理如下图。四个LUT的写数据端口DI1,DI2,写使能WE,写地址WA共用,称为写控制信号共用。读地址A分别控制。

的是MLX90640红外阵列传感器的底层驱动程序测试演示,是个完整的Keil工程,包含了EEPROM、寄存器和

(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。

是FPGA中常用的基础模块,可大范围的使用在缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章 FPGA片内

是FPGA中常用的基础模块,可大范围的使用在缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、EC

(刷新时除外)且速度很快,通常作为操作系统或其他正在运行中的程序的...

。本来的含义是:ROM是Read Only Memory的意思,也就是说这种存储器只能读,不能写。而

是Random Access Memory的缩写。这个词的由来是因为早期的计算机曾经使用磁鼓作为内存,而磁鼓和磁带都是典型的顺序

APB3是一个低功耗低成本接口。所有信号在时钟上升沿传输,每次传输需要两个时钟周期。

是一个多列的数据表格,其中每一列都是一个包含多个存储单元的块。通过在时钟的一次上升沿来读取

统计有效数据包的个数。 假设数据中存在pkt_id,pkt_id为0~63,则