光通信体系对更高的数据传输速率的需求一向增加,推动了对先进调制格局和高性能收发器的需求。要完成每波长 400Gbps 以上的数据传输速率,有远景的处理计划是选用杂乱的调制计划,如双偏振正交调幅(DP-QAM64)。这种调制格局经过为每个符号编码更多比特来供给更高的频谱功率,然后在电气和光学信道的有限带宽内完成更高的数据传输速率。

在本教程中,咱们将评论 Broadcom 规划和完成的 600Gbps DP-QAM64 相干光收发器前端,其特点是在 16nm CMOS 工艺中选用四个同步的 105GSps 8 位模数转化器 (ADC) 和四个数模转化器 (DAC)[1]。咱们将深入评论包含模数转化器、数模转化器和锁相环 (PLL) 在内的要害构建模块,并评论为完成高性能和高效运转而选用的立异技能。

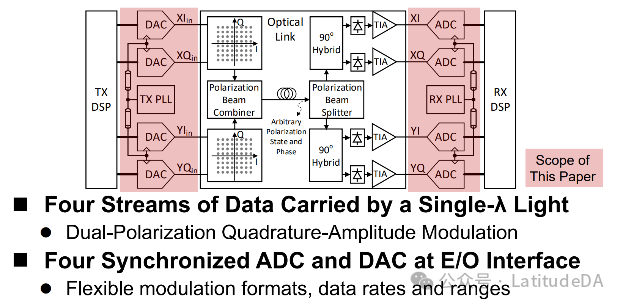

相干光收发器选用 DP-QAM 调制计划,经过单一波长的光收发数据。如图 1 所示,发射器由四个 DAC 组成,别离发生两个偏振(X 和 Y)的同相(I)和正交(Q)重量。这些信号经过偏振合束器组兼并调制到光载波上。

在接纳端,使用偏振分束器和 90 度混合器将光信号分红偏振重量。由此发生的四个信号(XI、XQ、YI、YQ)经过四个 ADC 转化回电域。数字化信号由数字信号处理(DSP)模块处理,以康复传输数据。

本文的重点是四个 ADC、四个 DAC 以及为转化器生成高速采样时钟的 PLL 的规划和完成。

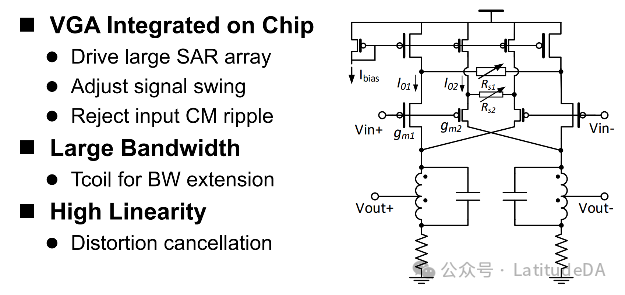

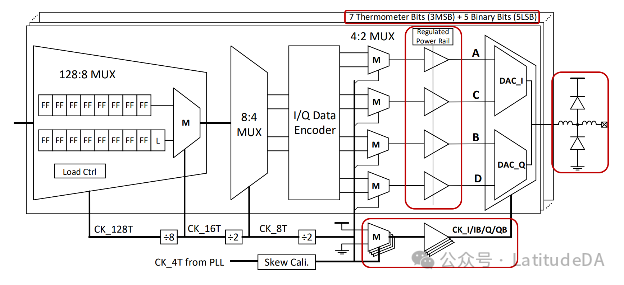

ADC 规划选用时刻交织架构,以完成 105GSps 的方针采样率。如图 2 所示,ADC 由 192 个单元逐次迫临寄存器 (SAR) ADC 组成,这些 ADC 选用两级盯梢坚持 (T/H) 电路进行时刻交织。输入信号首先由集成了失真消除电路的可变增益扩大器 (VGA) 扩大,以取得高线. ADC 框图

VGA 规划选用了新颖的失线 所示。两个差分对以相反的极性衔接,在坚持高增益的一起有用地消除了失真。这种消除技能依赖于器材尺度和电流的比率,因而对工艺、温度和电压改变不灵敏。

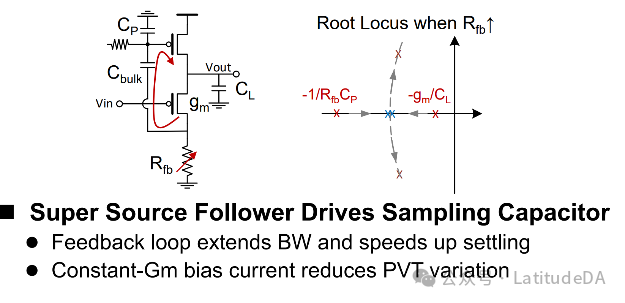

为了处理宽带 T/H 电路中的电容走漏问题,选用了超级源极跟从器 (SSF) 来驱动采样电容,如图 4 所示。SSF 集成了一个反应环路,可扩展带宽并加速沉积时刻,一起稳定 gm 偏置电流可削减 PVT 改变。

此外,如图 5 所示,使用具有电容抵消功用的差分采样开关,电容走漏效应得到了缓解。该技能可有用消除差分电容走漏,由此削减符号间搅扰 (ISI) 和频率纹波。

为了处理由 I/Q 时钟偏移和占空比失真引起的潜在交织尖峰,选用了片上校准环路。这些环路可保证 I 和 Q 时钟的准确对齐,以及准确的占空比校对,然后最大极限地削减特定频率下的交织脉冲。

如图 9 所示,经过带有大型缓冲器的两级时钟树完成了高效的大局时钟分配。每个缓冲器驱动一个 1.2 毫米的时钟通道,保证整个芯片的低偏移和低颤动时钟传输。

DAC 的带宽超越 35GHz,总谐波失真 (THD) 相当于 ENOB 超越 6 位(最高达 27GHz)(图 12)。SFDR 在 1GHz 时到达 51.6dB,在 25GHz 时到达 41.5dB(图 13)。

PLL 在 10kHz 至 100MHz 范围内完成了 51.4fs 的均方根 (RMS) 颤动,令人形象十分深入,这关于高速 ADC 和 DAC 坚持高 SNDR 很重要(图 14)。

该收发器前端可灵敏支撑各种调制格局和数据速率,适用于远程、城域和 ZR 使用,现在已投入量产。这一规划的成功实施为未来高速光收发器的开展排除了妨碍,以此来完成了更高的数据传输速率和更有用的光纤容量使用。