C的全体功用。鉴于此,本文将介绍这些非抱负要素发生的原因及常见的处理办法”

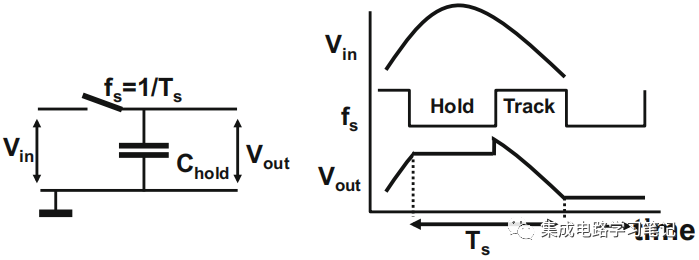

采样坚持电路通常被用在模数转换器规划中,起到信号收集的效果。图1是一个由开关和电容组成的采样坚持电路。在采样阶段,开关闭合且电容Chold收集输入信号的信息。在坚持阶段,开关断开Chold保存采样时间输入信号的信息,以此来完成信号的采样和坚持的功用。

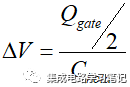

图1所示的采样坚持电路中的开关可由一个简略的MOS管完成。当开关导通时,沟道内存在电荷会堆集电荷Qgate。开关断开后,这些电荷会流出到采样电容上然后引起采样差错。这便是“电荷注入”。由电荷注入发生的差错可表示为

此外,时钟馈通效应也是引起采样差错的一个重要来历。MOS管的栅漏或栅源之间有交叠电容Cov。采样完毕时钟跳变时,会经过交叠电容馈通到采样电容上,然后引起采样差错。由时钟馈通而导致的差错可表示为

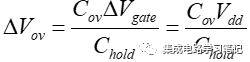

如图2所示,比较于图1添加了一个额定的虚拟开关。虚拟开关的状况与采样开关的状况相反,且巨细为采样开关的二分之一。当采样开关关断时,沟道电荷Qgate的一半流向输出端一侧,此刻虚拟开关敞开并吸收采样开关开释的剩余电荷。然后到达采样电容上的输入信号不被影响的意图。

该办法尽管简略但也存在必定的问题。采样开关不可能刚好向输出一侧注入一半的电荷。因而不能彻底按捺电荷注入所引起的差错。

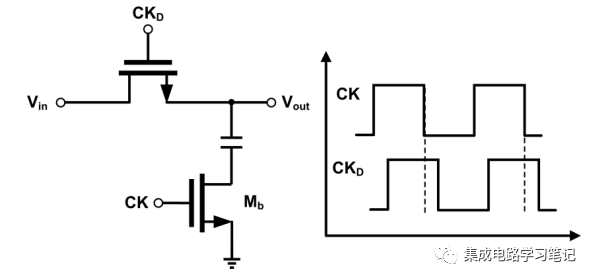

图3为底板采样技能的示意图。当采样完毕时,晶体管Mb首要断开,此刻采样电容下极板浮空,随后另一个晶体管再关断。由于采样电容下极板浮空处于高阻状况,晶体管内电荷不会流入采样电容上,然后防止电荷注入而引起的采样差错。值得一提的是,该结构没有办法处理时钟馈通的问题。

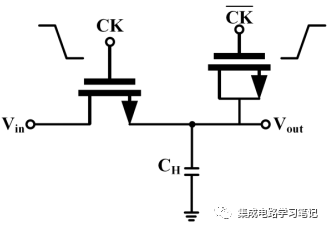

在规划中,差分是一种常见的消除偶次非线所示,实践采样电路中,不只有时钟馈通和沟道电荷注入等非抱负要素,输入信号经过MOS管的漏源寄生电容Cds(赤色标识)也会馈通到输出端。经过添加两个常关断的MOS开关巨细与采样开关共同,并结合差分结构能够轻松又有用的减小输入信号馈通的影响。

该差分结构相较于底板采样等办法具有采样精度高的长处,但这是以添加功耗和面积换来的。